# PEMBUATAN ANALOG DESIGN DAN LAYOUT IC (INTEGRATED CIRCUIT) AMPLIFER KELAS A

#### Machmud Effendy<sup>1</sup>

<sup>1</sup>Fakultas Teknik. Jurusan Elektro. Universitas Muhammadiyah Malang Alamat Koresondensi : Jl.Polowijen I No.192 Malang

#### ABSTRAK

The making of VLSI design ( Very Large Scale Integrated Scale Integration ) needed by planning of Analog Design and Layout. Where function of making of Analog Design is to translate the electric circuit becoming a verilog file which there are information about size of IC (integrated circuit) tha will be formed to use DSCH. While layout represent pattern form to be used in making of IC, where pattern form to be made have to pursuant to Analog Design which have been made and pursuant to power amplification value and its efficiency. The making of layout used MICROWIND software. Then its result will in test use program of winspice, so that characteristic of class A amplifier circuit can be seen graphly.

In this research is made analog design and layout for the circuit of amplifier class A, this matter is caused by this circuit still is often used in audio technology and radio, amplifier circuit of class A in the form of IC still seldom in selling marketing, and the last amplifier circuit of class A not to integrated to require compared to higher level energy dissipation which have integrated.

Key Word: Amplifier, Layout, IC

#### PENDAHULUAN

Perkembangan teknologi semikonduktor dalam tahun - tahun terakhir ini dapat digambarkan dalam hukum Moore (Ammar Mukheriee, 1986). dimana kapasitas suatu komponen elektronika dalam suatu chip mengalami peningkatan 4 kali dalam setiap 3 tahunnya. Beberapa faktor yang mempengaruhi peningkatan ini antara lain : bertambah kecilnya lebar jalur ( path ) pada komponen dasar dan yang menghubungkan antara beberapa komponen tersebut sehingga mengakibatkan terjadinya peningkatan resolusi pada teknik lithiography, bertambahnya jumlah silicon wafer sehingga mengakibatkan terjadinya peningkatan keandalan dalam proses fabrikasi, dan tersedianya perangkat lunak (software) untuk membuat logic design, layout, simulasi, verifikasi dan testing suatu design VLSI.

Dari penjelasan diatas, salah satu faktor yang membuat teknologi semikonduktor (dalam hal ini design VLSI) menjadi lebih banyak jumlah komponennya dalam satu chip adalah dengan adanya penggunaan perangkat lunak khusus yang digunakan untuk membuat logic design, layout, simulasi, verifikasi dan testing suatu design VLSI. Dalam penelitian sebelumnya (Machmud, 2005), perancangan gerbang logika dasar dan fungsi logika kombinational dapat dibuat layout IC nya menggunakan perangkat lunak DSCH dan Microwind. Dengan terbentuknya layout IC ini, maka akan terlihat pola ( patterning ) dan karakteristik dari IC yang akan dirancang. Namun, dalam penelitian ini masih menggunakan komponen – komponen digital yang masih belum diaplikasikan dalam rangkaian tertentu.

Oleh karena itu, dalam penelitian selanjutnya penulis akan merancang layout IC yang menggunakan komponen – komponen analog dan diaplikasikan dalam sebuah rangkaian amplifier kelas A. Kenapa diaplikasikan dalam rangkaian amplifier kelas A? alasan utamanya adalah untuk membuat rangkaian amplifier kelas A yang tidak terintegrasi dibutuhkan beberapa komponen transistor, resistor dan kapasitor. Rangkaian seperti ini mempunyai disipasi daya yang lebih tinggi jika

Machmud Effendy, Pembuatan Analog Desigen dan Layout ICDESIGN (Integrated Circuit) | 127 Amplifer Kelas A dibandingkan dengan rangkaian yang sudah terintegrasi dalam bentuk one chip IC.

Dalam penelitian ini juga bertujuan untuk mempermudah pembuatan analog design dan layout dalam proses desain VLSI menggunakan perangkat lunak DSCH dan MICROWIND, yang sebelumnya masih menggunakan cara manual, menyediakan salah satu bahan dasar dalam pembuatan IC amplifier kelas A dalam bentuk layout IC, mengetahui karakteristik dari IC yang sudah diketahui bentuk layoutnya ( rangkaian amplifier kelas A)

#### METODELOGI PENELITIAN

Penelitian ini merupakan penelitian yang bersifat eksperimen dalam bentuk simulasi dan perhitungan dengan tujuan untuk membuat analog design dan layout IC rangkaian amplifier kelas A, yang nantinya layout IC amplifer kelas A ini akan menjadi salah satu bahan dasar pembuatan IC amplifier kelas A.

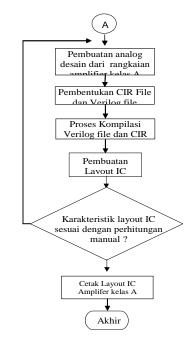

Metodologi penelitian yang digunakan untuk menyelesaikan pembuatan analog

Design dan layout IC ( Integrated Circuit ) Amplifier Kelas A., dapat kami

gambarkan dalam diagram alir berikut ini:

Gambar 1. Diagram Alir Penelitian

#### HASIL DAN PEMBAHASAN

bab ini berisi pembahasan tentang perencanaan dan pembuatan rangkaian analog amplifier kelas A menggunakan program DSCH dan pembuatan layout rangkaian amplifier kelas A menggunakan program MICROWIND. Pembahasan tersebut meliputi:

- 1. Pembuatan rangkaian analog amplifier kelas A satu tingkat dari komponen N-MOS, resistor dan kapasitor.

- 2. Menentukan parameter komponen N-MOS. resistor dan kapasitor sebegai pembentuk rangkaian amplifier kelas A

- 3. Melakukan perhitungan manual penguatan tegangan rangkaian amplifier kelas A.

- Pembuatan analog desain, verilog file dan CIR file

IC secara 3 dimensi.

# Pembuatan Analog Desain Rangkaian Amplifier kelas A

Rangkaian amplifer kelas A yang di buat dalam penelitian ini hanya satu tingkat, menggunakan komponen N-MOS, resistor dan kapasitor. Dimana fungsi dari N-mos adalah sebagai komponen utama yang berfungsi untuk menguatkan sinyal input, sedangkan resistor bergungsi untuk memberikan bias tegangan pada N-MOS dan memberikan arus pull up. Fungsi kapasitor adalah sebagai: Kopling (Penggandengan) yang berfungsi untuk meloloskan sinyal AC ( sinyal suara berbentuk sinusioda ) dan menahan sinyal DC dan juga sebagai buffer (menjembatani antar rangkaian).

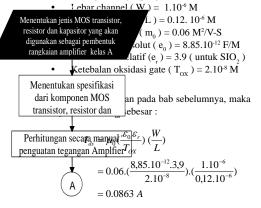

Sebelum membuat rangkaian amplifier kelas A secara utuh, maka akan ditentukna terlebih dahulu spesifikasi dari komponen N-MOS yang akan digunakan. Komponen N-MOS yang digunakan dalam pembuatan rangkaian amplifier kelas A satu tingkat ini memiliki spesifikasi sebegai berikut:

Manggunakan kondisi linier agar dapat Mulai agsi sebagai penguat.

Setelah nilai I, diketahui maka untuk mencari nilai penguatannya dibutuhkan paramater gm (

5. Pembuatan layout IC dan proses pembuatan transkonduktasni ) yang nilainya = Ids/Vgs, sehingga:

$$gm = \frac{I_{ds}}{V_{gs}}$$

$$= \frac{0.0863}{2}$$

$$= 0.043 \text{ S}$$

etelah mengetahui parameter gm. maka dibuatlah rangkaian amplifier kelas A menggunakan program DSCH seperti pada gambar berikut ini:

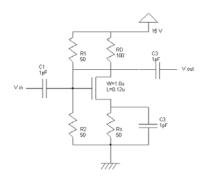

Gambar 2. Rangkaian amplifier kelas A

Dari rangkaian diatas dapat dijelaskan bahwa, Tegangan supply yang digunakan adalah 15 Volt DC. Sehingga tegangan keluarannya maksimal adalah sebesar tegangan supply (meskipun secara teori, nilai penguatannya dapat menghasilkan tegangan keluaran lebih besar dari tegangan supply). Untuk menghilangkan pengaruh sinyal AC pada komponen N-MOS, agar dapat bekerja pada kondisi DC, maka dibutuhkan kapasitor C3.

Komponen N-MOS telah di berikan nilai W sebesar 1 mikro meter dan nilai L sebesar 0.12

Selanjutnya adalah menghitung nilai penguatan dari rangkaian diatas, dimana nilai

Machmud Effendy, Pembuatan Analog Desigen dan Layout ICDESIGN (Integrated Circuit) | 129 Amplifer Kelas A

penguatan dari N-MOS adalah perkalian dari trankonduktansi ( gm ) dengan tahanan drain (  $\rm R_{\rm D}$  ), sehingga didapat :

$$A = \frac{V_{OUT}}{V_{IN}}$$

$$= gm. R_D$$

$$= 0.043.100$$

$$= 4.3 kali$$

Dari nilai penguatan diatas terlihat bahwa tegangan keluarannya sama dengan 4.3 kali dari tegangan masukannya.

Setelah rangkaian diatas terbentuk dan dihitung penguatannya, maka dengan menggunakan program DSCH juga, dibuat CIR file dan verilog file nya, agar dapat di bentuk layout IC nya. Berikut ini adalah CIR fike untuk rangkaian amplifier kelas A:

```

* Created 6/7/2009

```

\* Voltage and Current Sources

# VDD 1 0 DC 1.2

\*

\* Passive device

RD 3 1 100

R1 3 1 50

R2 0 3 50

Rs 0 2 50

C1 4 3 1 pF

C3 3 5 1 pF

C3 2 0 1 pF

\* Active devices

MN1 2 3 3 2 MN W=1.0u L=0.12 u

\* Node list

\* "Vdd" is node 1

\* "w1" is node 2

\* "w2" is node 3

\* "w3" is node 4

\* "w4" is node 5

\*

.TRAN 0.1 ns 250ns

\* Run simulation

\*# run

\*# set nobreak

\*# print > penguat.txt

\* show the result window

\*#plot

.Option DELMIN=0 RELTOL=1E-6

.end

Sedangkan daftar verilog filenya adalah sebagai berikut:

// DSCH 2.7a

// 6/7/2009 4:23:48 AM

$/\!/F:\machmud\desain\ vlsi\dschv2-7\dschv2-$

7\penguat.sch module penguat(); nmos nmos(w2,w1,w2);

// 1.0u 0.12u endmodule

// Simulation parameters in Verilog Format

// Simulation parameters

Dengan memasukkan nilai W dan L yang berbeda ( nilai W dan L lebih besar ) maka didapat hasil seperti dibawah ini :

$$I_{ds} = \mu_0 \left( \frac{\mathcal{E}_0 \mathcal{E}_r}{T_{OX}} \right) \left( \frac{W}{L} \right)$$

$$= 0.06. \left( \frac{8,85.10^{-12}.3.9}{2.10^{-8}} \right) . \left( \frac{2.10^{-6}}{1.10^{-6}} \right)$$

$$= 0.002 A$$

$$gm = \frac{I_{ds}}{V_{gs}}$$

$$= \frac{0.002}{2}$$

$$= 0.001 S$$

$$A = \frac{V_{OUT}}{V_{IN}}$$

$$= gm. R_D$$

$$= 0.001.100$$

$$= 1 kali$$

Dari hasil diatas dapat dijelaskan bahwa dengan berubahnya nilai W dan L maka perubahan penguatan menjadi cukup besar. Hasil CIR file dan verilog filenya adalah sebagai berikut:

\* Created 6/7/2009

\* Voltage and Current Sources

VDD 1 0 DC 1.2

\* Passive device

RD 3 1 100

R1 3 1 50

R2 0 3 50

Rs 0 2 50

C1 4 3 1 pF C3 3 5 1 pF

C3 2 0 1 pF

\* Active devices

MN1 2 3 3 2 MN W=2.0u L=1 u

\*

\* Node list

\* " Vdd" is node 1

\* "w1" is node 2 \* "w2" is node 3

\* "w3" is node 4

\* "w4" is node 5

.TRAN 0.1 ns 250ns

\* Run simulation

\*# run

\*# set nobreak

\*# print > penguat.txt

\* show the result window

\*#plot

.Option DELMIN=0 RELTOL=1E-6 .end

Sedangkan daftar verilog filenya adalah sebagai berikut:

```

// DSCH 2.7a

```

// 6/7/2006 4:23:48 AM

//F:\machmud\desain vlsi\dschv2-7\dschv2-

$7\polinim{penguat.sch}$ ; module penguat( ); nmos nmos(w2,w1,w2);

// 2u 1u endmodule

// Simulation parameters in Verilog Format

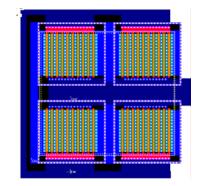

# Pembuatan Layout IC Rangkaian Amplifier kelas A

Pembuatan layout IC rangkaian amplifier kelas A didasarkan pada CIR file dan verilog file yang sudah terbentuk sebelumnya. Sehingga pembuatan layout menggunakan program mirowind ini tergantung dari rangkaian sebelumnya yang dibentuk menggunakan program DSCH yang menghasilkan CIR file dan verilog file.

Untuk menghasilkan layout IC menggunakan program microwind, maka pertama – tama harus di kompilasi verilog file yang sudah terbentuk sehingga muncul menu kompilasi seperti dibawah ini :

Gambar 3. Menu kompilasi verilog file

Dari gambar 9, terlihat bahwa hasil kompilasi tidak terjadi kesalahan, sehingga verilog yang di kompilasi dapat dilanjutkan untuk dibuat layoutnya seperti berikut ini:

Gambar 4. Layout IC Rangkaian Amplifier kelas A.

Machmud Effendy, Pembuatan Analog Desigen dan Layout ICDESIGN (Integrated Circuit) | 131 Amplifer Kelas A Gambar layout IC diatas dapat dijelaskan bahwa, terdapat Vin dan Vout yang dapat digunakan untuk paramter simulasi. Untuk menampilkan simulasi tegangan masukan dan tegangan keluaran dari layout IC ditas, maka masih menggunakan program MICROWIND dengan mengklik Simulate – Run Simulation – Voltage Vs Time.maka akan tampil simulasi Vin dan Vout sebagai berikut:

Gambar 5. Simulasi gelombang sinusoida input dan output

Dari hasil simulasi pada gambar 6.6, memperlihatkan bahwa terjadi penguatan tengangan masukan. Dimana besar tegangan masukannya sebesar 2.34 Volt menjadi tegangan keluaran sebesar 10.2 Volt. Sehingga terjadi penguatan tegangan sebesar 4.36 kali. Nilai penguatan ini tidak jauh beda denga nilai penguatan tegangan berdasarkan perhitungan manual sebesar 4.3 kali.

Dilihat dari persamaan sebelumnya, terlihat bahwa nilai penguatan tegangan pada amplifier kelas A hanya tergantung pada nilai W (lebar channel), L (panjang channel),  $T_{\rm ox}$  (ketebalan oksidasi) dan nilai  $R_{\rm ox}$  (tahanan drain).

# Proses 3 Dimensi Pembuatan Layout IC Amplifier Kelas A

Setelah mengetahui layout IC dan hasil simulasi penguatan tegangan yang dimiliki oleh IC amplifier kelas A, maka untuk lebih menggambarkan proses pembuatan layout IC tersebut, digunakan simulasi proses 3 dimensi pembuatan IC amplifier kelas A. Seperti pada pembuatan layout IC, program Microwind masih digunakan untuk simulasi proses 3 dimensi pembuatan layout IC ini, dengan cara klik Simulate

- Process steps in 3 D, maka akan muncul proses 3 dimensi seperti dibawah ini:

Gambar 6. Proses 3 dimensi pembuatan IC amplifier kelas A

Secara umum dari proses 3 dimensi pembuatan IC amplifier kelas A terdapat 10 proses dalam pembuatan IC tersebut antara lain :

- Initial Substrate

Proses ini berfungsi untuk menyiapkan bahan dasar dari IC yang berasal dari SIO<sub>2</sub> dengan jenis P-type.

- b. P++ Epitaxy

- Untuk memberikan perlindungan (protection) pada lapisan substrate dari sinar ultraviolet yang digunakan pada selanjutnya, maka diperlukan lapisan epitaxy.

- c. N- Diffusion

- Pada proses N-diffusion ini terjadi penetrasi doping jenis N-type pada lapisan epitaxy, dimana proses ini berfungsi untuk memasukkan doping boron, phospor kedalam lapisan epitaxy.

- d. Thin Oxide Growth

- Untuk mencegah adanya korosi dan kontaminasi dari bahan metal lain, maka diperlukan lapisan oksidasi yang berasal dari silica. Proses ini membtuhkan pemanasan sampai ratusan derajat celcius. Perlu diketahui bahwa tebal dari lapisan hanya maksimal 40.10<sup>-10</sup> meter.

- e. Polysilicon deposit

Sedangkan untuk melindungi lapisan substrate

dan epitaxy dari bahan anorganic pada saat

dipanaskan, maka dibutuhkan polysilicon deposit. Pada proses ini terdapat dua cara yaitu vacuum evaporation (menggunkan ruang hampa udara) dan sputtering (tidak menggunakan ruang hampa udara, namun menggunakan proses pengadukan dengan kecepatan yang sangat tinggi), dimana masing – masing proses mempunyai kelebihan dan kekurangan masing – masing.

- f. N+ Impalantation

- Proses implantasi jenis N+ ini berfungsi untuk 4. memasukkan impurity jenis N kedalam lapisan oksidasi.

- g. P+ Implantation

- Seperti pada proses sebelumnya, proses ini juga berfungsi untuk memasukkan impurity 5. jenis P ke dalam lapisan oksidasi.

- h. 2<sup>nd</sup> Polysilicon deposit

- Proses perlindungan terhadap lapisan substrate dan epitaxy dilakuan dua kali, hal ini untuk lebih membersihkan kedua lapisan dari bahan anorganic yang tidak diinginkan.

- i. Create Contact

- Proses ini berfungsi untuk menghubungkan antara *hole* (lubang) yang telah di beri doping dan impurtity. Bahan contact yang digunakan adalah jenis metal.

- j. Etching.

- Metal contact yang terbentuk pada proses diatas, ternyata sebagian harus dihilangkan agar tidak terjadi penumbukan metal. Untuk menghilangkan metal ini digunakan proses Etching menggunakan HF dan H<sub>4</sub>PO<sub>4</sub>.

#### KESIMPULAN DAN SARAN

Dari hasil pembuatan analog desain dan layout IC amplifier kelas A menggunakan program DSCH dan MICROWIND, maka dapat diberikan beberapa kesimpulan sebagai berikut :

- Dengan adanya program DSCH, maka pembuatan analog design dapat dilakukan dengan mudah sekaligus juga dapat langsung disimulasikan secara visual sehingga mempermudah dalam pembuatan desain VLSI.

- Skematik yang dibuat dengan program DSCH dapat diubah menjadi menjadi sebuah verilog

- file dan CIR file, yang nantinya file ini dapat dijadikan masukan dalam pembuatan layout menggunakan program MICROWIND.

- . Karakterisktik dari rangkaian amplfier kelas A dapat diketahui langsung secara visual dengan cara merubah beberapa parameter komponen utamanya (N-MOS) antara lain: width (lebar channel), length (panjang channel) dan Tox (ketebalan lapisan oksidasi).

- . Semakin besar nilai lebar channel, maka nilai penguatan tegangannya semain besar pula, sebaliknya semakin besar nilai ketebalan oksidasi gate, maka nilai penguatan tengangannya semakin kecil.

- Proses pembuatan IC amplifier kelas A juga dapat di gambarkan secara 3 dimensi, sehingga mempermudah dalam mengetahui proses pembuatan IC tersebut.

### DAFTAR PUSTAKA

- Albert Paul Malvino, "Prinsip prinsip dasar eletronika I", Erlangga, 1998.

- Ammar Mukherjee, "Introduction to NMOS and CMOS VLSI System Design", Prentice Hall, 1986

- Andrew Brown, "VLSI Circuit And System In Silicon", Mc Graw Hill, 1991.

- Etienne Sicard, "Manual of DSCH and MICROWIND versi 2,7". Insa DGEI, 2003.

- Etinne Sicard, " *Class A Power Amplifier*:, Insa DGEI, 2003.

- James E. Buchanan, BiCmos / CMOS System Design, Prentice Hall, 1997

- Machmud, " Otomatisasi Pembuatan Logic Design dan Layout IC", P2I-UMM, 2005

- Neil H.E Weste and Kamran Eshraghlan, "

Principles of CMOS VLSI Design", Addison

Wesley Publishing Company, 1993.

Machmud Effendy, Pembuatan Analog Desigen dan Layout ICDESIGN (Integrated Circuit) | 133 Amplifer Kelas A